Informações Preliminares

É fortemente sugerido que, antes de iniciar a montagem do Kraft 80, leia todas as instruções eté o final para evitar o risco de problemas ao longo da montagem.

Itens necessários

São os seguintes:

- Placa Kraft 80

- Diagrama Esquemático

- Materiais: ver lista aqui

- Uma fonte de 5 volts por 1 ampere (no ML vende várias bem baratas, é bom conferir se a saída está com a voltagem correta

antes de usar):

Montagem - Passos Iniciais

A primeira etapa é configurar a PCI do Kraft 80 para o modo KRAFT 80. Isto é feito soldando-se os jumpers de configuração como mostrado abaixo:

| JP7 | ABERTO |

| JP8 | 1-2 |

| JP9 | 1-2 |

| JP10 | 1-2 |

| JP11 | 1-2 |

| JP12 | 1-2 |

| JP13 | 1-2 |

| JP14 | ABERTO |

| JP15 | 1-2 |

| JP16 | 1-2 |

| JP17 | 1-2 |

| JP18 | 1-2 |

| JP19 | 1-2 |

| JP20 | 1-2 |

Montagem - Componentes

A grande maioria dos componentes pode ser montada sem grande observações, bastando seguir o esquema. Alguns, no entanto podem pedir um pouco mais de atenção:

- Jumpers:

- JP1 e JP2: Molex 3 pinos

- Ligam a energia dos LEDs da Porta A. Posicione o fecho nos pinos 1-2 para ligar.

- JP3 e JP4: Molex 3 pinos - Selecionam o mapa de memória:

- Pinos 2-3 ativam 48k RAM + BIOS com o ROM BASIC. Inicialmente adote esta configuração.

- Pinos 1-2 ativam 56k RAM + BIOS sem o ROM BASIC.

- JP1 e JP2: Molex 3 pinos

- Capacitor eletrolítico: C6 - 100uF

- Nesta posição faltou a marca do '+', o lado positivo deve ser montado próximo ao letreiro 'C6' na placa.

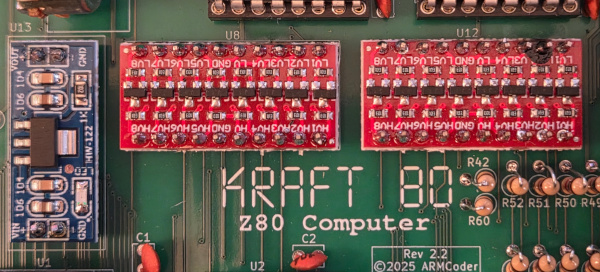

- Conversores U8, U12 e U13:

- U8 e U12 são conversores de nível para interfacear o FPGA e a CPU. As linhas HV ficam voltadas para o lado da CPU, e as linhas LV ficam voltadas para o lado do FPGA.

- U13 é um conversor de tensão para alimentar o FPGA (e alguns outros circuitos) com 3,3 volts. Atente para os lados VIN e VOUT, estão marcados na placa.

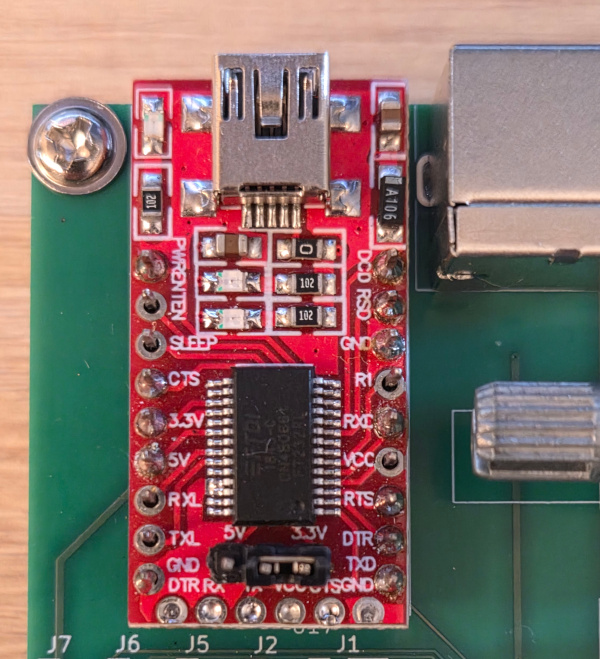

- U17:

- Este é um conversor USB para TTL-SERIAL. Ele possui internamente um pequeno jumper que pode ser selecionado entre 5V e 3,3V. Selecione a posição 3,3V.

Montagem - Display

O display requer atenção especial por dois motivos:

- Alguns displays encontrados no mercado podem ser diferentes, mecanicamente, do espaço dimensionado na placa.

- São necessários espaçadores e arruelas de papelão para fazer o suporte adequado do display.

Se por sorte o display for do tipo "conector embaixo", basta soldar uma barra de pinos reta e montar os espaçadores. Para saber o tipo do display, olhe o lado de trás e gire o display para que os letreiros fiquem orientados "de pé".

Este display é do tipo "conector em cima" e não pode ser montado com conector de pinos retos na placa. |

Este display é do tipo "conector embaixo" e pode ser montado com conector de pinos retos na placa. |

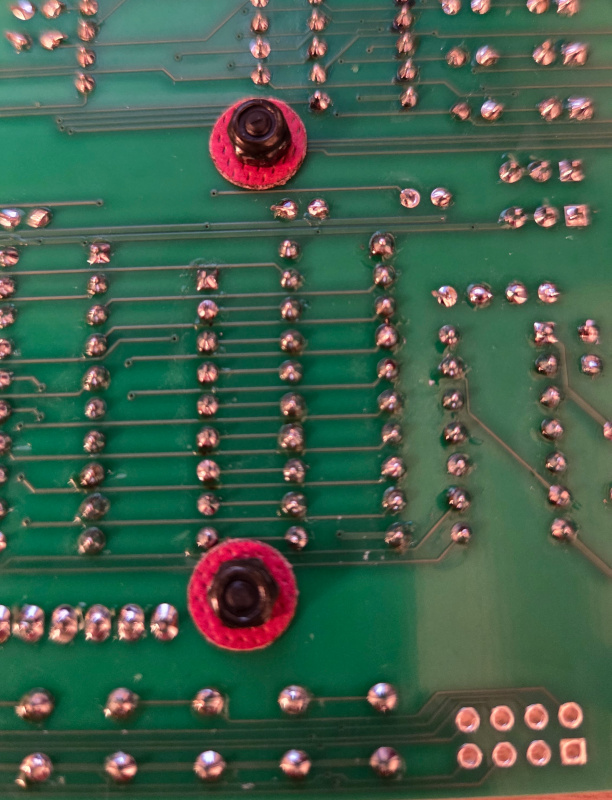

Espaçadores do Display

São necessários quatro espaçadores M2.5 de 10 a 12mm de comprimento e arruelas de papelão M2.5 ou M3.

As arruelas podem ser precisas para completar a altura dos espaçadores, eles ficam um pouquinho abaixo da altura do display quando ele é montado com barra de pinos, pelo menos com o espaçador de 10mm.

Outra utilidade das arruelas é proteger as trilhas do lado de baixo da placa. Isso porque dois dos espaçadores ficaram perigosamente perto das trilhas, e a porca pode entrar em contato e danificar essas trilhas (ver foto abaixo). Infelizmente foi um erro de desenho da placa que não percebi antes.

|

Preparação das ROMs

O Kraft 80 possui duas ROMs, sendo:

- ROM Monitora: Esta ROM é necessária para o funcionamento do Kraft 80. Possui o código de boot, os drivers do Hardware, o BIOS e

o Kraftmon.

É montada no soquete de alavanca (U2).

A imagem desta ROM pode ser baixada aqui. - ROM BASIC: Opcional. Possui a implementação da linguagem BASIC.

É montada no soquete U18.

A imagem desta ROM pode ser baixada aqui.

Preparação do Módulo FPGA

O FPGA precisa ser programado para funcionar com o Kraft 80.

O método recomendado é usar

o programa OpenFPGALoader. Basicamente, conecta-se o módulo FPGA no computador

com um cabo USB-C e se faz a gravação com este programa.

A imagem que deve ser gravada no FPGA pode ser baixada aqui.

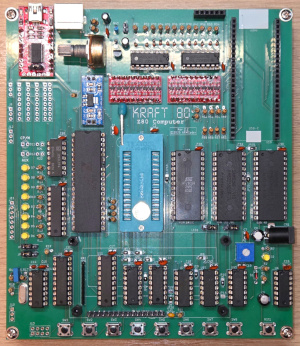

Montagem Concluída

Na imagem abaixo pode-se ver a placa totalmente montada mas sem o display e o FPGA, para facilitar a visualização (clique na imagem para ampliar).

|

Ligando a Placa

Antes de tudo, verifique toda a montagem. Uma boa limpeza e verificação das soldas da placa são recomendáveis antes de continuar.

Conecte a EEPROM no soquete U2 e o FPGA na posição U19, atentando para a marca de orientação (chanfro) no encapsulamento do integrado.

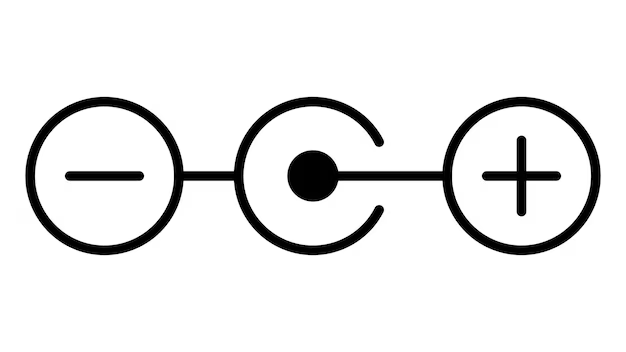

Energia: A tensão deve ser de 5 volts DC estabilizados e a polaridade deve respeitar o diagrama abaixo (positivo no centro):

|

Nem pense em descuidar da alimentação, uma voltagem errada ou polaridade invertida podem causar um dano massivo aos componentes do aparelho! Não diga que eu não avisei.